7.3.2 8251功能特点

7.3.2 8251功能特点

Intel 8251是Intel 8250串行接口芯片的改进型,具有同步、异步接收或发送(USART)的功能,使用单+5V电源和单相时钟的28脚双列直插封装。

1.8251内部结构

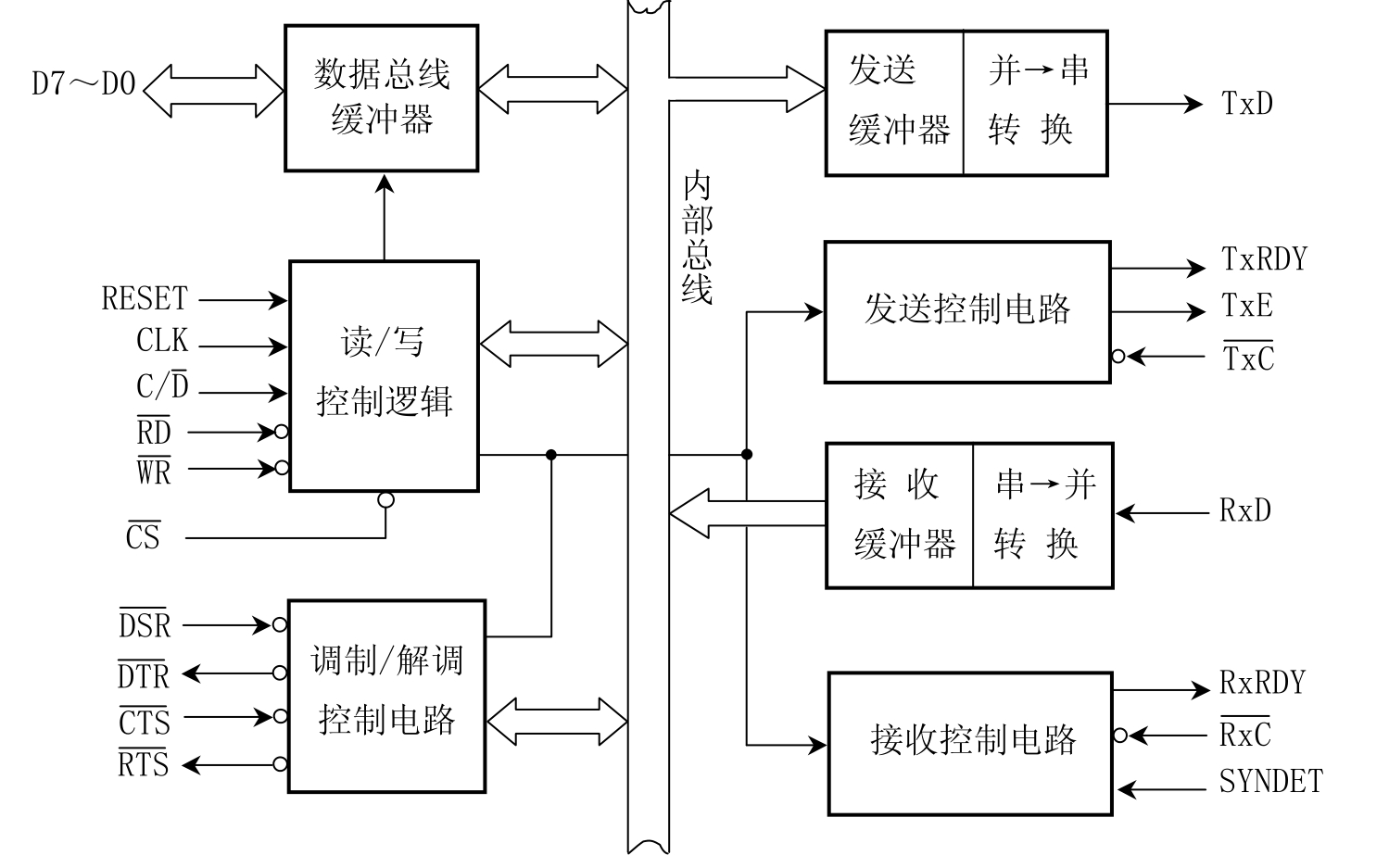

8251A的内部结构如图7.9所示,它由接收缓冲器、接收控制电路、发送缓冲器、发送控制电路、调制/解调控制电路、读/写控制逻辑和数据总线缓冲器等七个部分构成。

图7.9 8251A内部结构框图

① 数据总线缓冲器:三态双向8位缓冲器,它使8251A与系统总线连接起来。来自CPU的控制命令和发送的字符经过缓冲器进入8251A内部,8251A内部的状态信息、接收的数据也经过缓冲器送到系统总线。

② 读/写控制逻辑电路:接收CPU的各种控制信息,从而确定本次操作的方式,如 表示CPU向8251A写入控制字或数据;

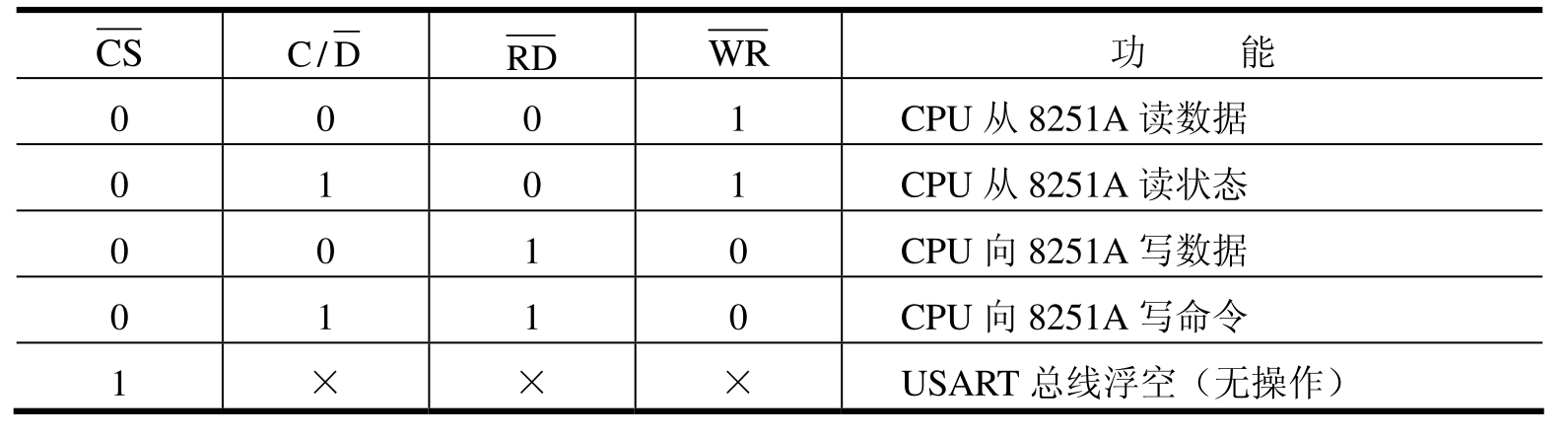

表示CPU向8251A写入控制字或数据; 表示CPU读取8251A的数据或状态信息等。8251A读写操作如表7-2所示。

表示CPU读取8251A的数据或状态信息等。8251A读写操作如表7-2所示。

表7-2 8251A读写操作表

③ 调制/解调控制电路:当进行远程通信时,需要使用调制/解调器。8251A的调制/解调电路提供一组通用的控制信号,使8251A可以直接与调制解调器相连,完成远程通信。

④ 发送缓冲器:由数据发送缓冲器和并→串移位寄存器组成。发送数据时按发送要求,将数据变成串行数据经TxD发送出去。

⑤ 发送控制电路:协调发送缓冲器工作,为同步、异步串行传送提供识别信息,如起始位、同步字等。

⑥ 接收缓冲器:从RxD接收串行数据,并按照相应的格式转换成并行数据。

⑦ 接收控制电路:协调接收缓冲器工作,分离出接收的数据等。

2.8251A工作方式

8251A可用于同步和异步串行通信,但其工作方式不完全相同。

(1)异步接收方式:在异步方式,当允许接收且准备好接收数据时,8251A监视RxD线。在没有信号时为高电平,一旦检测到RxD线为低电平,即认为是起始位到达,便启动内部计数器开始计数,当计数到一个数据位宽度的一半(若时钟频率为波特率的16倍时,则计数到第8个脉冲)时,再次采样RxD线,若仍然为低电平,则确认是一个起始位,否则是干扰信号。

在起始位检测到后,每隔一位数据宽度的时间,在接收脉冲 的上升沿采样一次RxD线作为数据位,送入串→并移位寄存器。在移位寄存器中,数据被转换为并行数据,并进行奇偶校验以及去掉停止位后,经8251A内部数据总线送到接收缓冲器,同时发出RxRDY信号,表示一个数据接收完成。

的上升沿采样一次RxD线作为数据位,送入串→并移位寄存器。在移位寄存器中,数据被转换为并行数据,并进行奇偶校验以及去掉停止位后,经8251A内部数据总线送到接收缓冲器,同时发出RxRDY信号,表示一个数据接收完成。

(2)异步发送方式:当初始化编程时,置1发送允许位TxEN,在 时可进行异步发送。发送时,发送器自动为每个字符加上起始位,并根据要求加上校验位和停止位,在发送时钟

时可进行异步发送。发送时,发送器自动为每个字符加上起始位,并根据要求加上校验位和停止位,在发送时钟 的下降沿经发送移位寄存器从TxD线发出。

的下降沿经发送移位寄存器从TxD线发出。

(3)同步接收方式:在单同步方式下,8251A监视RxD线,每出现一个数据位就把它移一位,然后把接收寄存器与含有同步字符的寄存器比较,如果相同则表示接收方和发送方已同步,接收方使SYNDET=1;如果不同则需接收下一个数据进行比较。

在实现同步后,通信双方进行数据传送,8251A利用接收时钟采样和移位RxD线的数据位,按规定的位数装配成并行数据送到数据总线缓冲器,并发出RxRDY信号,告知CPU已经接收到一个有效数据。

(4)同步发送方式:同步发送在TxEN=1和 时开始,发送器在准备发送的数据前插入程序设定的一个或两个同步字符,在数据中插入校验位,在发送时钟

时开始,发送器在准备发送的数据前插入程序设定的一个或两个同步字符,在数据中插入校验位,在发送时钟 的作用下,将数据一位一位地发送出去。

的作用下,将数据一位一位地发送出去。

在数据传送过程中,可能会出现CPU来不及将新的字符输出给8251A的情况,为使字符间没有间隙,8251A会自动在TxD线上插入同步字符。